¿Qué Es La Memoria Caché Del Procesador? Características.

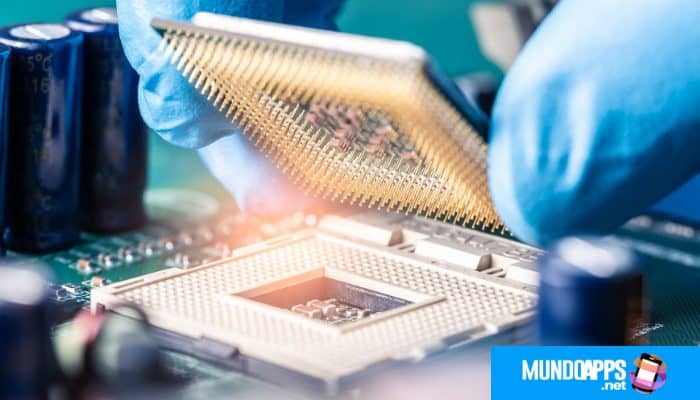

Probablemente todos los que tienen alguna idea de lo que es un procesador, conocen la presencia de cualquier procesador con memoria caché. Además, los procesadores modernos compatibles con x86 para computadoras portátiles y de escritorio no solo tienen un caché, sino un sistema completo de jerarquía de memoria caché, incluida la memoria caché del primer, segundo e incluso tercer nivel, que se encuentran en el procesador. En este blog te explicaremos todo sobre qué es la memoria caché del procesador.

Pero, ¿por qué un procesador necesita un caché y en qué se diferencia un caché de otro? No todos los usuarios de PC pueden responder a estas preguntas. Y la pregunta de por qué se crean varios cachés de diferentes niveles y si no es más fácil crear uno grande puede desconcertar incluso a muchos usuarios experimentados que están versados en hardware. Entonces, si no sabe cómo responder las preguntas enumeradas, este artículo será de su interés.

También puedes leer: ¿Qué Es La Placa Base? 3 Formatos De La Placa Base Más Conocidos.

¿Qué es la memoria caché del procesador?

La caché es una memoria ultrarrápida que utiliza el procesador para almacenar temporalmente los datos más utilizados Así es como, en definitiva, se puede describir este tipo de memoria. La caché es una memoria integrada en el procesador, en la que se escriben los datos (comandos) de RAM más utilizados, lo que acelera significativamente el trabajo.

La memoria caché está construida sobre flip-flops que, a su vez, están formados por transistores. Un grupo de transistores ocupa mucho más espacio que los condensadores que componen la memoria RAM. Esto trae consigo muchas dificultades en la producción, así como limitaciones en el volumen. Es por eso que la memoria caché es una memoria muy cara, aunque tiene volúmenes insignificantes.

Pero de tal estructura, la principal ventaja de tal memoria es la velocidad. Dado que los disparadores no necesitan ser regenerados, y el tiempo de retardo de las válvulas en las que están ensamblados es corto, el tiempo para cambiar el disparador de un estado a otro ocurre muy rápidamente. Esto permite que la memoria caché funcione a las mismas frecuencias que los procesadores modernos.

Propósitos de la memoria caché

La forma más sencilla de responder a la pregunta es por qué necesita memoria caché. Como sabes, el procesador trabaja con datos almacenados en RAM. Sin embargo, la velocidad de la memoria y el procesador son significativamente diferentes: si el procesador se comunica directamente con la memoria principal (lectura o escritura), se utiliza para la mayor parte del tiempo simplemente estaría inactivo.

Es para reducir los retrasos en el acceso a la RAM que se utiliza la memoria caché, que es mucho más rápida en comparación con la RAM. De hecho, si la RAM se usa para suavizar los retrasos en el acceso a los datos en una unidad (HDD, SSD o memoria flash), entonces el caché del procesador se usa para nivelar los retrasos en el acceso a la RAM.

En este sentido, la RAM puede verse como una caché de almacenamiento. Sin embargo, hay una diferencia muy seria entre la RAM y la caché del procesador: la caché del procesador es completamente transparente para el programador, es decir, los datos que contiene no pueden tratarse mediante programación.

La SRAM estática

Opera a frecuencias de varios gigahercios sin problemas, es decir, una caché basada en dicha memoria puede operar a la frecuencia de reloj del procesador. La DRAM dinámica funciona a frecuencias significativamente más bajas.

Por ejemplo, la frecuencia efectiva de la DRAM DDR3 más común en la actualidad es de 1600 MHz. Sin embargo, esta es precisamente la frecuencia de memoria efectiva, es decir, la frecuencia con la que se alimentan los datos al bus externo en el modo de acceso a paquetes, mientras que la frecuencia real del núcleo de la memoria es de solo 200 MHz.

Por supuesto, estamos interesados principalmente en la frecuencia de memoria efectiva, es decir, 1600 MHz o 1,6 GHz. Parecería que esto es mucho, pero es necesario tener en cuenta los tiempos de memoria, que caracterizan su latencia.

Además, los tiempos de memoria se determinan en ciclos de reloj del núcleo de memoria y no en ciclos de reloj de la frecuencia efectiva. es decir, para la memoria DDR3-1600 con una frecuencia de memoria de 200 MHz, cada ciclo de reloj es 1/200 MHz = 5 ns. Al mismo tiempo, un ciclo de procesador con una frecuencia de, por ejemplo, 3 GHz dura solo 0,3 ns, es decir, 17 veces menos.

Recuerda que los tiempos de memoria son retrasos medidos en ciclos de reloj del núcleo de memoria entre instrucciones individuales. Se asignan varios tiempos de memoria, correspondientes a los retrasos entre diferentes comandos. Los tiempos más importantes son el retardo de RAS a CAS (tRCD), la latencia de CAS (tCL), el retardo de activo a precarga (tRAS) y la precarga de RAS (tRP).

La temporización del TRC

Determina el retraso mediante el comando ACTIVE de la línea de memoria deseada y mediante el comando WRITE o READ data. El intervalo de tiempo tCL transcurre desde el comando para leer (escribir) datos y hasta que el primer elemento de datos se envía al bus (escribir datos en una celda de memoria). Cada elemento de datos subsiguiente aparece en el bus de datos en el siguiente ciclo de reloj (con acceso a paquetes).

El final del ciclo de acceso al banco de memoria se realiza emitiendo el comando PRECHARGE, que conduce al cierre de la línea de memoria. El intervalo de tiempo tRP debe transcurrir desde el comando PRECHARGE hasta la llegada del comando de activación de la nueva línea de memoria.

Y el lapso de tiempo mínimo desde el momento en que se emite el comando de activación de línea hasta que el comando PRECHARGE, que cierra la línea de memoria, se llama tRAS. Los tiempos de la memoria principal generalmente se escriben en la siguiente secuencia: tCL-tRCD-tRP-tRAS.

¿Cómo funciona la memoria caché del procesador?

La caché consta de un controlador y la memoria caché real. El controlador de caché gestiona el funcionamiento de la memoria caché, es decir, carga los datos necesarios de la RAM en ella y devuelve, cuando es necesario, los datos modificados por el procesador a la RAM. Arquitectónicamente, el controlador de caché se encuentra entre el procesador y la memoria principal (Fig. 1).

Al interceptar las solicitudes a la RAM, el controlador de caché determina si hay una copia de los datos solicitados en la caché. Si existe una copia de este tipo, esto se llama un acierto de caché; en este caso, los datos se recuperan muy rápidamente del caché (mucho más rápido que de la RAM). Si los datos requeridos no están en la caché, entonces hablan de una falla en la caché, entonces la solicitud de datos se redirige a la RAM.

Para lograr el mayor rendimiento, las pérdidas de efectivo deben ocurrir con la menor frecuencia posible (idealmente, ausentes). Teniendo en cuenta que la capacidad de la memoria caché es mucho menor que la RAM, esto no es tan fácil de lograr.

Por lo tanto, la tarea principal del controlador de caché es cargar la memoria caché con los datos realmente necesarios y eliminar de manera oportuna los datos que ya no se necesitan. Es importante entender que la caché siempre está "llena", ya que es irracional dejar parte de la memoria caché vacía.

Video recomendado: ¿Que es la Memoria Cache y como funciona? Procesadores, CPU

Políticas de reemplazo de caché

Como ya se mencionó, la caché siempre está llena y los datos nuevos ingresan solo reemplazando los datos antiguos. Los algoritmos que determinan la estrategia de reemplazo de datos son diferentes. El algoritmo más simple, no dotado de inteligencia, es un algoritmo de selección aleatoria, cuando los datos a reemplazar se seleccionan aleatoriamente (Random).

Está claro que la política de sustitución basada en el algoritmo de elección arbitraria es simple de implementar, pero ineficiente y, por lo tanto, no se utiliza en los procesadores modernos (estamos considerando solo procesadores compatibles con x86).

La decisión de reemplazar los datos en la caché también se puede tomar sobre la base del análisis de la frecuencia de acceso a los datos (menos utilizado, LFU), cuando en primer lugar se reemplazan los datos con la frecuencia de acceso más baja.

La política de reemplazo basada en el análisis de frecuencia de hits requiere que haya contadores en cada línea de caché (hablaremos más adelante sobre qué es una línea de caché), que se actualizan en cada solicitud exitosa.

El siguiente algoritmo posible para determinar la política de reemplazo es el algoritmo LRU (menos usado recientemente), cuando se reemplazan los datos a los que no se ha accedido durante más tiempo. El algoritmo FIFO (Primera entrada, primera salida) o LRR (Menos reemplazado recientemente) también es posible, cuando se reemplazan los datos que se cargaron antes que cualquier otra persona.

Estrategias de almacenamiento en caché

Hemos analizado los algoritmos en los que se basan las políticas de reemplazo de caché de datos, y ahora hablemos de los algoritmos que subyacen a la estrategia de almacenamiento en caché, es decir, los algoritmos para cargar la caché con datos.

Recuerde que la tarea principal del controlador de caché es llenar el caché con datos actualizados y minimizar el número de pérdidas de caché. De hecho, para esto, el controlador de caché debe saber o poder predecir qué datos necesitará el procesador en el futuro y, en base a esto, cargarlos en el caché con anticipación (carga preventiva de datos).

Está claro que "seguro" el controlador de caché no sabe nada y no posee ninguna inteligencia sobrenatural, y por lo tanto, aunque es raro, ocurren fallas de efectivo. Existen varias estrategias para colocar datos en la memoria caché.

La estrategia más simple y poco inteligente es que el acceso a la RAM (con la posterior colocación de una copia de los datos en el caché) ocurre solo si los datos solicitados por el procesador no están en el caché (hay deslizamientos de caché). Esta estrategia se denomina almacenamiento en caché bajo demanda.

Existen varios algoritmos para la carga especulativa proactiva de datos en la caché. El algoritmo más simple se basa en la suposición de que los datos de la memoria principal se procesan secuencialmente, en orden ascendente de direcciones.

Es decir, el controlador de caché simplemente carga no solo los datos solicitados por el procesador en el caché desde la RAM, sino también los datos vecinos en orden ascendente de direcciones. Si los datos se procesan de manera secuencial, las solicitudes posteriores del procesador darán como resultado un acierto de caché.

También puedes leer: Que Es Una Memoria Virtual (Sistemas Operativos)

Comprensión de la asociatividad de la memoria caché

Hasta ahora, no hemos considerado exactamente cómo se asigna la RAM a la memoria caché. Dado que la unidad mínima de información con la que trabaja el caché es la línea del caché, dividamos condicionalmente toda la RAM en bloques (líneas) del mismo tamaño que las líneas del caché. En aras de la simplicidad, supongamos que el caché tiene ocho líneas de largo y la RAM tiene 24 líneas de caché.

Enumeremos todas las líneas para que la numeración comienza desde 0. Es decir, en la memoria caché el último número de línea es 7, y en la memoria principal - 23. Surge la pregunta: ¿cómo vincular las líneas de la memoria principal con las líneas de la caché? Es decir, si, por ejemplo, necesita cargar la primera línea de RAM en el caché, ¿en qué línea del caché se cargará? Aquí es donde son posibles varias opciones.

Memoria caché totalmente asociativa

La primera y más sencilla opción es que cualquier línea de RAM se puede escribir en cualquier línea de la memoria caché. Es decir, cada línea de la memoria caché se puede asociar con cualquier línea de RAM y viceversa (Fig. 4). Esta memoria caché se denomina totalmente asociativa.

Una caché completamente asociativa tiene pros y contras. Su principal desventaja es que buscar información en él mediante una etiqueta de cadena requiere una implementación de hardware compleja y, por lo tanto, es bastante costosa. De hecho, para determinar si los datos solicitados por el procesador están en la memoria caché, es necesario iterar sobre todas las líneas de la caché.

La búsqueda de la línea de caché deseada puede llevar cientos de ciclos, lo que hará que la memoria caché sea ineficiente. Por lo tanto, en el caso de una caché totalmente asociativa, debe implementar la visualización simultánea en paralelo de todas las etiquetas, lo cual es bastante difícil de hacer.

Y en términos de consumo de energía, ver todas las etiquetas en paralelo no es la mejor solución. Esta es la razón por la que las memorias caché completamente asociativas no pueden ser grandes.

Caché de visualización directa

Otra opción para organizar el mapeo de RAM a la memoria caché es lo opuesto al caché completamente asociativo considerado. Esta es la llamada caché de asignación directa, cuando cada línea de RAM no corresponde a ninguna, sino solo a una línea estrictamente definida de memoria caché.

En este caso, cada línea de RAM está asociada con solo una línea de memoria caché, y cada línea de memoria caché corresponde a varias líneas de RAM, pero nuevamente, no a ninguna, sino a las estrictamente definidas.

Caché asociativo de composición tipográfica

Una opción intermedia entre una caché totalmente asociativa y una caché de asignación directa es la caché de N vías (caché de N vías). Tal caché consta de varios bancos (segmentos) independientes, cada uno de los cuales es un caché mapeado directamente, y los propios bancos son completamente asociativos con respecto a la RAM.

Es decir, cualquier elemento de la memoria de acceso aleatorio puede ubicarse en cualquier banco de memoria de efectivo, pero dentro del banco corresponde a una línea de caché estrictamente definida.

Coherencia de caché

La coherencia de la memoria caché se refiere al algoritmo que garantiza la coherencia del contenido de la RAM y la memoria caché. Asegurar la coherencia de la memoria caché es una tarea muy importante que realiza el controlador de caché. Si la memoria principal estuviera disponible solo para lectura, entonces la copia de los datos en la memoria caché siempre coincidiría con los datos originales en la memoria principal.

Sin embargo, la RAM también está disponible para escritura, lo que plantea el problema de la modificación oportuna de datos en la RAM. De hecho, se puede acceder a la RAM no solo por el procesador, sino también por dispositivos periféricos, y en procesadores multiprocesador y multinúcleo, diferentes procesadores o núcleos.

Digamos que un dispositivo periférico u otro procesador accede a una determinada celda de memoria que ya se ha modificado en la caché, pero que aún no se ha intercambiado en la memoria principal. En este caso, el controlador de caché debe actualizar primero el contenido de la celda de RAM correspondiente, de lo contrario se leerán datos irrelevantes desde allí.

Asimismo, si un dispositivo periférico u otro procesador cambia el contenido de una celda RAM, el controlador de caché debe averiguar si las celdas modificadas están cargadas en su caché y, de ser así, deben actualizarse. Es decir, debe realizar un seguimiento oportuno de los cambios en los datos de la memoria caché y la RAM y sincronizar estos cambios para mantener la coherencia entre la memoria caché y la RAM.

Organización de caché en capas

Todos los procesadores modernos tienen al menos una estructura de caché de dos niveles, y la mayoría de los procesadores Intel tienen una memoria caché de tres niveles. Se hace una distinción entre una caché de primer nivel (denominada L1), una caché de segundo nivel (L2) y una caché de tercer nivel (L3).

Además, en el caso de los procesadores Intel, las memorias caché de todos los niveles se encuentran en la matriz del procesador.

Parecería, ¿por qué necesitas hacer tantos cachés? ¿No es más fácil crear una gran caché? No resulta más fácil. El problema es que cuanto mayor es el tamaño de la caché, menor es su velocidad. Es decir, puede hacer un caché grande pero lento, o puede hacer varios cachés pequeños pero rápidos, y la segunda opción resulta ser más preferible.

Además, los cachés en diferentes niveles del procesador realizan diferentes tareas. Por lo tanto, la caché L1 más rápida y pequeña siempre se divide en una caché de datos (L1D) y una caché de instrucciones o instrucciones (L1I). Esta es la denominada arquitectura de procesador de Harvard. La caché L1 siempre pertenece solo a un núcleo de procesador específico.

La caché L2

Ya está unificada (contiene datos e instrucciones). La caché L2 siempre es más grande que la caché L1, pero más lenta. En el caso de los procesadores de múltiples núcleos, la caché L2 pertenece a un núcleo de procesador específico.

Pero la caché L3 es la más grande y lenta y se comparte entre todos los núcleos del procesador (en la arquitectura del procesador Intel). Está claro que en el caso de que el procesador tenga un sistema de memoria caché multinivel, es necesario organizar la interacción entre cachés de diferentes niveles.

Comencemos por mirar un sistema de caché de dos niveles. Dicha memoria caché se basa en una de dos arquitecturas: incluida, que también se llama inclusiva, y exclusiva, llamada exclusiva. Es decir, la caché L2 siempre se construye en una arquitectura inclusiva o excluyente con respecto a la caché L1 (ten en cuenta que si hay una caché L3, las cachés L2 y L1 pueden ser no inclusivas o no exclusivas entre sí).

Una caché L2 inclusiva siempre duplica el contenido de una caché L1, por lo que la capacidad efectiva de la caché es igual a la capacidad de la caché L2. Una caché L2 exclusiva nunca duplica el contenido de una caché L1, por lo que la capacidad efectiva de la caché es igual a la capacidad total de las cachés L1 y L2.

También puedes leer: Cómo Saber Qué Tarjeta Gráfica Tengo

Deja una respuesta